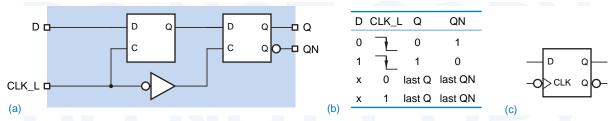

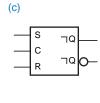

**Figure 7-18** Negative-edge triggered D flip-flop: (a) circuit design using D latches; (b) function table; (c) logic symbol.

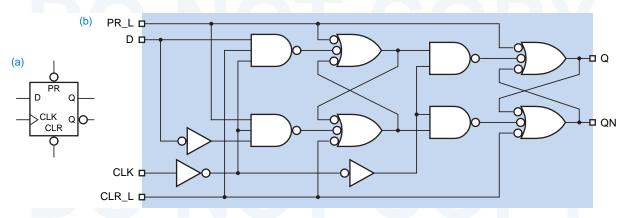

inputs on an SR latch. The logic symbol and NAND circuit for an edge-triggered D flip-flop with these inputs is shown in Figure 7-19. Although asynchronous inputs are used by some logic designers to perform tricky sequential functions, they are best reserved for initialization and testing purposes, to force a sequential circuit into a known starting state; more on this when we discuss synchronous design methodology in \secref{syncmethod}.

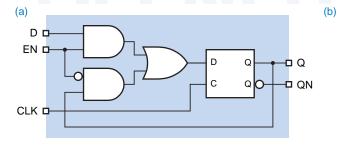

## 7.2.6 Edge-Triggered D Flip-Flop with Enable

A commonly desired function in D flip-flops is the ability to hold the last value stored, rather than load a new value, at the clock edge. This is accomplished by adding an *enable input*, called EN or CE (*clock enable*). While the name "clock enable" is descriptive, the extra input's function is not obtained by controlling

enable input clock-enable input

**Figure 7-19** Positive-edge-triggered D flip-flop with preset and clear: (a) logic symbol; (b) circuit design using NAND gates.

TIME FOR A COMMERCIAL

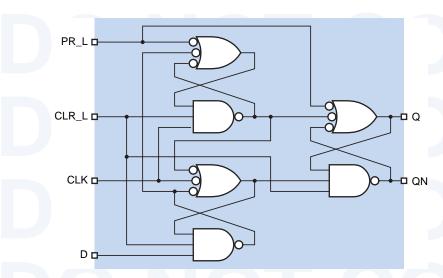

Commercial TTL positive-edge-triggered D flip-flops do not use the master-slave latch design of Figure 7-15 or Figure 7-19. Instead, flip-flops like the 74LS74 use the six-gate design of Figure 7-20, which is smaller and faster. We'll show how to formally analyze the next-state behavior of both designs in Section 7.5.

Figure 7-20 Commercial circuit for a positive-edgetriggered D flip-flop such as 74LS74.

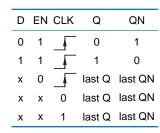

the clock in any way whatsoever. Rather, as shown in Figure 7-21(a), a 2-input multiplexer controls the value applied to the internal flip-flop's D input. If EN is asserted, the external D input is selected; if EN is negated, the flip-flop's current output is used. The resulting function table is shown in (b). The flip-flop symbol is shown in (c); in some flip-flops, the enable input is active low, denoted by an inversion bubble on this input.

## 7.2.7 Scan Flip-Flop

An important flip-flop function for ASIC testing is so-called *scan capability*. The idea is be able to drive the flip-flop's D input with an alternate source of data during device testing. When all of the flip-flops are put into testing mode, a test pattern can be "scanned in" to the ASIC using the flip-flops' alternate data inputs. After the test pattern is loaded, the flip-flops are put back into "normal" mode, and all of the flip-flops are clocked normally. After one or more clock ticks, the flip-flops are put back into test mode, and the test results are "scanned out."

scan capability

**Figure 7-21** Positive-edge-triggered D flip-flop with enable: (a) circuit design; (b) function table; (c) logic symbol.

Copyright © 1999 by John F. Wakerly

1 0 EN CLK Q O-

(c)

Copying Prohibited

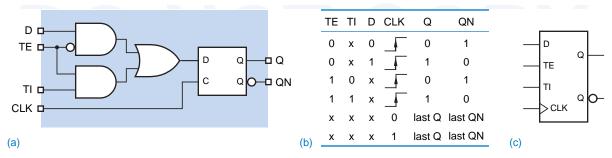

**Figure 7-22** Positive-edge-triggered D flip-flop with scan: (a) circuit design; (b) function table; (c) logic symbol.

Figure 7-22(a) shows the design of a typical scan flip-flop. It is nothing more than a D flip-flop with a 2-input multiplexer on the D input. When the TE (*test enable*) input is negated, the circuit behaves like an ordinary D flip-flop. When TE is asserted, it takes its data from TI (*test input*) instead of from D. This functional behavior is shown in (b), and a symbol for the device is given in (c).

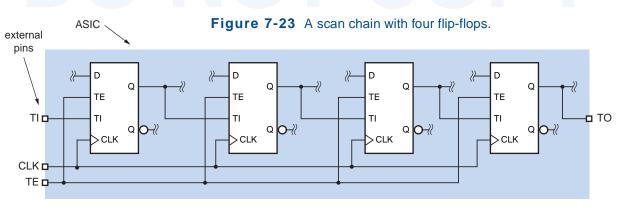

The extra inputs are used to connect all of an ASIC's flip-flops in a *scan chain* for testing purposes. Figure 7-23 is a simple example with four flip-flops in the scan chain. The TE inputs of all the flip-flops are connected to a global TE input, while each flip-flop's Q output is connected to another's TI input in serial (daisy-chain) fashion. The TI, TE, and TO (test output) connections are strictly for testing purposes; the additional logic connected to the D inputs and Q outputs needed to make the circuit do something useful are not shown.

To test the circuit, including the additional logic, the global TE input is asserted while n clock ticks occur and n test-vector bits are applied to the global TI input and are thereby scanned (shifted) into the n flip-flops; n equals 4 in Figure 7-23. Then TE is negated, and the circuit is allowed to run for one or more additional clock ticks. The new state of the circuit, represented by the new values in the n flip-flops, can be observed (scanned out) at TO by asserting TE while n more clock ticks occur. To make the testing process more efficient, another test vector can be scanned in while the previous result is being scanned out.

Copyright © 1999 by John F. Wakerly

Copying Prohibited

test-enable input, TE test input, TI scan chain

There are many different types of scan flip-flops, corresponding to different types of basic flip-flop functionality. For example, scan capability could be added to the D flip-flop with enable in Figure 7-21, by replacing its internal 2-input multiplexer with a 3-input one. At each clock tick, the flip-flop would load D, Tl, or its current state depending on the values of EN and TE. Scan capability can also be added to other flip-flop types, such as J-K and T introduced later in this section.

## \*7.2.8 Master/Slave S-R Flip-Flop

We indicated earlier that S-R latches are useful in "control" applications, where we may have independent conditions for setting and resetting a control bit. If the control bit is supposed to be changed only at certain times with respect to a clock signal, then we need an S-R flip-flop that, like a D flip-flop, changes its outputs only on a certain edge of the clock signal. This subsection and the next two describe flip-flops that are useful for such applications.

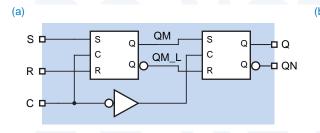

If we substitute S-R latches for the D latches in the negative-edge-triggered D flip-flop of Figure 7-18(a), we get a *master/slave S-R flip-flop*, shown in Figure 7-24. Like a D flip-flop, the S-R flip-flop changes its outputs only at the falling edge of a control signal C. However, the new output value depends on input values not just at the falling edge, but during the entire interval in which C is 1 prior to the falling edge. As shown in Figure 7-25, a short pulse on S any time during this interval can set the master latch; likewise, a pulse on R can reset it. The value transferred to the flip-flop output on the falling edge of C depends on whether the master latch was last set or cleared while C was 1.

Shown in Figure 7-24(c), the logic symbol for the master/slave S-R flip-flop does not use a dynamic-input indicator, because the flip-flop is not truly edge triggered. It is more like a latch that follows its input during the entire interval that C is 1, but that changes its output to reflect the final latched value only when C goes to 0. In the symbol, a *postponed-output indicator* indicates that the output signal does not change until enable input C is negated. Flip-flops with this kind of behavior are sometimes called *pulse-triggered flip-flops*.

master/slave S-R flip-flop

postponed-output indicator pulse-triggered flip-flop

**Figure 7-24** Master/slave S-R flip-flop: (a) circuit using S-R latches; (b) function table; (c) logic symbol.

| o) |   |   |         |        |         |

|----|---|---|---------|--------|---------|

| •  | S | R | С       | Q      | QN      |

|    | Х | Х | 0       | last Q | last QN |

|    | 0 | 0 | $\prod$ | last Q | last QN |

|    | 0 | 1 | $\prod$ | 0      | 1       |

|    | 1 | 0 | $\prod$ | 1      | 0       |

|    | 1 | 1 | Л       | undef. | undef.  |

|    |   |   |         |        |         |

<sup>\*</sup>Throughout this book, optional sections are marked with an asterisk.